# **Defect Tolerance and Nanomechanics in Transistors that Use Semiconductor Nanomaterials and Ultrathin Dielectrics**\*\*

By Jong-Hyun Ahn, Zhengtao Zhu, Sang-Il Park, Jianliang Xiao, Yonggang Huang, and John A. Rogers\*

This paper describes experimental and theoretical studies of the mechanics of free-standing nanoribbons and membranes of single-crystalline silicon transfer printed onto patterned dielectric layers. The results show that analytical descriptions of the mechanics agree well with experimental data, and they explicitly reveal how the geometry of dielectric layers (i.e., the width and depth of the features of relief) and the silicon (i.e., the thickness and widths of the ribbons) affect mechanical bowing (i.e., "sagging") in the suspended regions of the silicon. This system is of practical importance in the use of semiconductor nanomaterials for electronic devices, because incomplete sagging near defects in gate dielectrics provides a level of robustness against electrical shorting in those regions which exceeds that associated with conventional deposition techniques for thin films. Field effect transistors formed using silicon nanoribbons transferred onto a range of ultrathin gate dielectrics, including patterned epoxy, organic self-assembled monolayers, and HfO<sub>2</sub>, demonstrate these concepts.

## 1. Introduction

Interest in flexible, large area electronics and circuits for applications in consumer electronics, sensors, and medical devices has experienced recent and rapid growth.<sup>[1-4]</sup> As a materials approach to these kinds of systems, we have developed a technology to generate micro- and nanoscale objects of single-crystalline inorganic semiconductors using conventional microfabrication techniques with bulk or layered wafer substrates. In the case of silicon, micro/nanoribbons can be prepared from standard silicon-on-insulator (SOI) or bulk silicon (111) wafers by lithography and etching processes.<sup>[5,6]</sup> In this class of material, which we refer to as microstructured silicon ( $\mu$ s-Si), the typical thicknesses are between 50 and

[\*] Prof. J. A. Rogers, Dr. Z. Zhu, S.-I. Park Departments of Materials Science and Engineering Beckman Institute and Frederick Seitz Materials Research Laboratory University of Illinois at Urbana-Champaign Urbana, IL 61801 (USA) E-mail: jrogers@uiuc.edu Prof. J.-H. Ahn School of Advanced Materials Science and Engineering SKKU Advanced Institute of Nanotechnology, Sungkyunkwan University Suwon 440-746 (Korea) Prof. Y. Huang Departments of Civil and Environmental Engineering and Mechanical Engineering, Northwestern University Evanston, IL 60208 (USA) I. Xiao

Department of Mechanical Engineering, Northwestern University Evanston, IL 60208 (USA) 500 nm, resulting in excellent mechanical bendability and the ability to integrate with nontraditional device substrates, such as thin plastic sheets for flexible electronics. Other similar elements can be formed from GaAs, GaN, InP using conceptually related "top-down" approaches.<sup>[7,8]</sup> For the purpose of device integration, we use a dry transfer printing technique to relocate the semiconducting objects from the mother wafer to a target substrate, where an element of a soft elastomer such as poly(dimethylsiloxane) (PDMS) provides the stamp.<sup>[9]</sup> With this materials and integration strategy, it is possible to create electronics on unusual substrates (e.g., plastic sheets, plates of glass) in two or three dimensional heterogeneous layouts, with device and circuit performance approaching that of conventional wafer-based technologies.<sup>[10-12]</sup> Related methods to similar systems,<sup>[13,14]</sup> as well as strategies that involve printing of solution suspensions of wires, rods, and other solid structures<sup>[15-17]</sup> are also of interest.

A unique feature of all of these types of approaches is that the key materials are delivered to the target substrate in the form of solid objects. This procedure is much different than conventional thin film strategies where the deposition process involves vapor or fluid transport of atomic or molecular species to the substrate. These differences are of both fundamental and practical importance. For example, small solid objects can span gaps and defects in the substrate, forming bridging structures that thereby reduce the sensitivity to surface roughness and thin film pinhole defects. This paper explores the relevant physics of this type of mechanics, through comprehensive experiment and theory. In particular, it studies the mechanics of bowing, or "sagging," in µs-Si ribbons that span trenches and gaps on patterned dielectric structures. Examples of the utility of this mechanics are illustrated through the fabrication of high performance field effect transistor devices that use

<sup>[\*\*]</sup> This work was supported by the Department of Energy (DE-FG02-07ER46471) and used the Center for Microanalysis of Materials of the Frederick Seitz Materials Research Laboratory supported by the Department of Energy (DE-FG02-07ER46453 and DE-FG02-07ER46471).

FULL PAPER

ultrathin gate dielectrics, with high levels of naturally occurring and engineered structural defects.

## 2. Results and Discussion

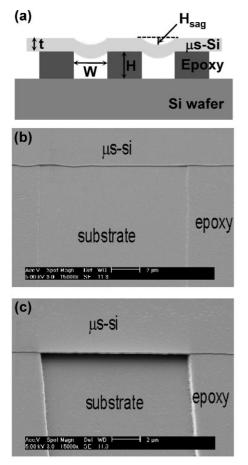

Figure 1a shows schematic illustrations of structures of  $\mu$ s-Si ribbons printed on layers of epoxy with lithographically defined trenches where the epoxy was completely removed. The ribbons can mechanically bow or "sag" in the regions of the trenches due to external loads such as gravity, or due to generalized adhesion forces such as electrostatic force and Van der Waals interactions between the ribbons and the underlying substrate. Electrostatics are most important when there is a significant difference in potential between the ribbons and the substrate.<sup>[18]</sup> Our AFM measurement conditions involve

**Figure 1.** Thin ribbons of silicon printed onto patterned layers of epoxy. a) Cross-sectional schematic illustration, with definitions of key variables. b) and c) Scanning electron micrographs of ribbons of silicon completely collapsed (i.e., sagged) b) and perfectly suspended c) across a lithographically defined trench in a layer of epoxy with thickness of 54 and 749 nm, respectively.

electrically grounding this system to minimize these effects, although we cannot rule out their role. Such sagging phenomena depend on the thickness of the epoxy (*H*), the width of the trench (*W*), and the thickness (*t*) of the  $\mu$ s-Si ribbons, as illustrated in Figure 1a. For example, the ability of the ribbons to bridge the trench without complete sagging increases with the thickness of epoxy. Figure 1a and b show, as examples, cases of complete sagging (Fig. 1a; H=54 nm;  $W=10 \,\mu$ m;  $t=100 \,\mu$ m;  $t=100 \,\mu$ m;  $t=100 \,\mu$ m; t=100 nm) and negligible sagging (Fig. 1b;  $H=749 \,\mathrm{nm}$ ;  $W=10 \,\mu$ m;  $t=100 \,\mathrm{nm}$ ), which correspond to  $H_{\mathrm{sag}}=H$  and  $H_{\mathrm{sag}}=0$ , respectively.

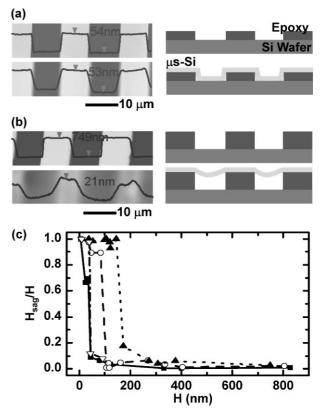

To evaluate the physics of this sagging process and its origins, we printed  $\mu$ s-Si ribbons on patterned epoxy lines with different heights and line widths. Figure 2a shows AFM images patterns of epoxy with H = 54 nm height, and  $W = 10 \,\mu$ m (in line and space patterns, where the widths of the epoxy regions

Figure 2. Sagging of thin ribbons of silicon on patterned lines of epoxy lines with different heights and spacings. a) Atomic force micrographs of a patterned layer of epoxy (top; thickness, H = 54 nm) and a similar structure with a 100 nm thick layer of silicon printed on top (bottom). The cartoon illustrations show these two different cases (right). These data indicate that the silicon is in a completely sagged state in the regions of the trenches. b) Atomic force micrographs of a patterned layer of epoxy (top; thickness, H = 749 nm) and a similar structure with a 100 nm thick layer of silicon printed on top (bottom). The cartoon illustrations show these two different cases (right). These data indicate that the silicon is in a nearly perfectly suspended state in the regions of the trenches. c) Plot of  $H_{sag}/H$  as a function of H for different trench widths (W), where the widths are equal to the spacing between the trenches. Filled squares:  $W = 2 \mu m$ ; open circles:  $W = 5 \mu m$ ; filled up-triangle:  $W = 10 \,\mu m$  wide. Open down-triangle:  $W = 10 \,\mu m$  wide. For all cases, the thickness of the silicon is 100 nm, except for the open downtriangles, which correspond to a silicon thickness of 290 nm.

were equal to their spacings), before and after printing µs-Si ribbons with thicknesses of 100 nm. Linecuts through the AFM images show surface profiles with height variations of 54 and 53 nm before and after printing, respectively, indicating that the ribbons sag completely down to substrate, corresponding to  $H_{\text{sag}} = H$ . We believe that the sagging occurs immediately after printing. We used negligibly small applied pressures during printing to minimize mechanical strains that could cause sagging. By contrast, the surface profiles for µs-Si ribbons on epoxy with H = 749 nm, with otherwise similar W and layouts,  $H_{\rm sag} = 21 \, \rm nm$ , indicating that the ribbons are substantially suspended over the trenches (Fig. 2b). Figure 2c presents the ratio of  $H_{sag}$  to H as a function of H for W ranging from 2 to 10 µm. This ratio approaches 1 for the case of complete sagging and 0 for perfect suspension. As W increases, the ribbons undergo complete sagging on structures with progressively larger values of H. Of particular note is the abruptness of the transition between complete sagging and perfect suspension. This behavior is reminiscent of the snap-down characteristics observed in microelectromechanical devices.<sup>[19]</sup> For example, ribbons with t = 100 nm sag at H = 10 nm and  $W = 2 \mu m$ , and at H = 84 nm and  $W = 5 \mu$ m, respectively (Fig. 2c). In addition, thick Si ribbons of t = 290 nm tend to sag at lower H than thin ribbons of t = 100 nm.

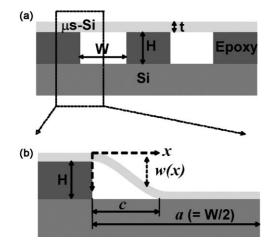

The physics can be understood through analytical treatments of the mechanics. Figure 3 illustrates the geometry of the system that was analyzed. The function w(x) describes the profile sagging (i.e., w(x) is zero at x = 0 and is H at x = c). The maximum value of w(x) is equal to the previously defined quantity  $H_{\text{sag}}$ . The total energy,  $U_{\text{total}}$  for displacement (i.e., sagging) of the suspended ribbon is related to the deformation energy and the adhesion energy by

$$U_{\text{total}} = U_{\text{deformation}} - U_{\text{adhesion}} \tag{1}$$

We assume here that the influence of gravity is negligible.<sup>[20]</sup> The validity of this assumption is examined at the end of

**Figure 3.** Schematic diagrams that define key variables for the theoretical analysis.

the analysis. In Eq. (1), the deformation energy,  $U_{deformation}$ and the adhesion energy,  $U_{adhesion}$  can be obtained from the bending rigidity,  $\overline{E}_{Si}I_{Si}$  [ $\overline{E}_{Si} = E_{Si}/(1 - v_{Si}^2)$ ,  $E_{Si}$  and  $v_{Si}$  the Young's modulus and Poisson's ratio of Si,  $I_{Si} = t^3/12$ , and t is the thickness] as  $U_{deformation} = \int_0^c \frac{1}{2}\overline{E}_{Si}I_{Si}[w(x)^n]^2 dx$  and from the adhesion energy per unit area,  $\gamma$  between  $\mu$ s-Si and substrate as  $U_{adhesion} = (a - c)\gamma$ , respectively. If  $U_{total}$  at ground state is considered as zero, ribbon starts sagging when  $U_{total}$  is less than zero.

$$U_{\text{total}} = \int_{0}^{c} \frac{1}{2} \overline{E}_{\text{Si}} I_{\text{Si}} [w(x)'']^2 dx - (a-c)\gamma \le 0$$

(2)

Minimization of total energy  $\partial U_{\text{total}}/\partial c = 0$  with respect to unsagged length, c gives

$$c = \left(\frac{3\overline{E}_{\rm Si}t^3H^2}{2\gamma}\right)^{\frac{1}{4}}\tag{3}$$

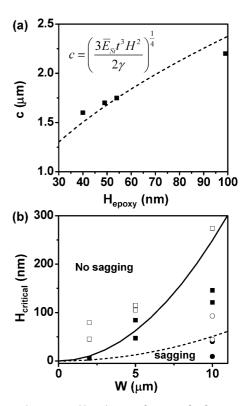

We can fit the experimental data to determine the adhesion energy,  $\gamma$ , using this equation. Figure 4a shows the unsagged length, c as a function of H for  $W = 10 \,\mu\text{m}$  and  $t = 100 \,\text{nm}$  to fit the adhesion energy,  $\gamma$  per unit area between Si and  $\mu$ s-Si. The

**Figure 4.** a) The unsagged length, *c* as a function of *H* for  $W = 10 \mu$ m and 100 nm thick Si ribbons measured experimentally (squares) and calculated theoretically where the adhesion energy ( $\gamma$ ) per unit area was used as a single fitting parameter. b) Comparison of critical sagging height calculated from theoretical models with experimental results. The solid and dotted lines denote calculation results for 100 and 290 nm Si ribbons, respectively. The squares and the circles denote experimental results for 100 and 290 nm Si ribbons, respectively; open (suspending) and filled (sagging).

FULL PAPER

squares and the line denote measured data and result fitted from Eq. (3), respectively. For  $E_{\rm si} = 130$  GPa and Poisson's ratio,  $v_{\rm si} = 0.27$ ,  $\gamma$  is 66 mJ m<sup>-2</sup>, which is comparable to literature values.<sup>[21]</sup>

There exists a critical thickness of epoxy,  $H_{\text{critical}}$  at which the deformation energy and the adhesion energy are equal (i.e., the starting point of  $H_{\text{sag}}/H=1$ ), which is given by

$$H_{\text{critical}} = \frac{3\sqrt{6}}{64} W \sqrt{\frac{\gamma W^2}{\overline{E}_{Si}t^3}}$$

(4)

This equation predicts that  $H_{\text{critical}}$  is proportional to the square of W. We can estimate  $H_{\text{critical}}$  as a function of W using  $\gamma$ obtained from Figure 4a and Eq. (4) as shown in Figure 4b. For comparison of calculated to experimental results, we plotted the stable sagged and suspended configurations because it is difficult to define directly the critical point in experiment. The solid and dotted lines denote results calculated for 100 and 290 nm thick µs-Si ribbons, respectively. The solid squares and circles denote the stable sagged configurations from experimental results for 100 and 290 nm µs-Si ribbons, respectively, and the open squares and circles denote the suspended configurations. It is seen that the sagged and suspended regions agree well with predicted values. In the actual system, the sagging mechanics can be affected by factors such as environmental conditions, surface roughness, and surface treatment.<sup>[18,21]</sup> For example, a hydrophobic Si substrate coated with organosilane can exhibit lower adhesion. The surface roughness can also decrease the adhesion.<sup>[22]</sup>

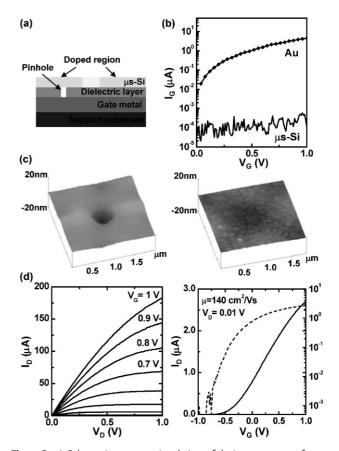

The ability of the  $\mu$ s-Si ribbons to span gaps, trenches, and pinholes creates opportunities for building transistor devices that are extremely tolerant to structural defects in gate dielectric layers, of the type that would cause catastrophic failure in conventional thin film devices. To illustrate this capability, we built transistors using printed Si ribbons on epoxy dielectrics with intentionally patterned pinhole "defects." Figure 5a shows a schematic illustration of a device structure and patterned dielectric. In devices that we examined, the channel lengths and widths were 7 and 100  $\mu$ m, respectively. The silicon and epoxy thicknesses were 100 and 25 nm, respectively. A sheet of PET coated with ITO provided the substrate and the gate electrode.

The 25 nm thick layers of epoxy formed in the manner used here show large leakage currents, as illustrated by the filled squares in Figure 5b, which corresponds to current that flows between a film of Au (thickness = 100 nm, width = 100  $\mu$ m) evaporated directly onto the epoxy and the underlying ITO. This behavior contrasts with the case for currents measured through similar structures, but with the Au layer replaced with transfer printed layer of Si with doped contacts (t = 100 nm, width = 100  $\mu$ m, channel = 7  $\mu$ m) where the gate leakage current is close to the noise limits in our setups (i.e., ~0.1 nA). This result indicates that the Si can span not only lithographically defined trenches but also those intrinsic to spin cast films.

Figure 5c shows an AFM image of a region of a dielectric intentionally patterned with defects in the form of circular

**Figure 5.** a) Schematic cross-sectional view of device structures of transfer-printed  $\mu$ s-Si on ultrathin dielectric layers. The pinhole represents an idealized view of a type of structural defect that can occur naturally or that can be introduced for the purpose of demonstration. b) Comparison of leakage currents measured in capacitor structures that consist of Au (top) and printed, Si (bottom) with doped contact on a 25 nm thick layer of epoxy dielectric film on an ITO (100 nm)/PET (180  $\mu$ m) substrate. The ability of the Si to suspend over pinhole defects contributes to dramatically lower leakage compared to evaporated Au. c) Atomic force micrographs of a thin epoxy dielectric with a lithographically defined hole through its thickness before (left) and after (right) transfer printing of a layer of Si (*t* = 100 nm) on top. d) Electrical characteristics of a transistor with channel length and width of 7 and 100  $\mu$ m, respectively: typical current–voltage characteristics (left) and linear and log scale plots of transfer curves collected at  $V_p = 0.01V$  (right).

holes with diameters of 1 µm that extend completely through the thickness of the epoxy to the underlying ITO. This image shows that the silicon is perfectly suspended over this hole, thereby avoiding electrical shorting to the ITO. Figure 5d shows electrical characteristics of an µs-Si transistor having this design. The effective device mobilities, calculated using standard models,<sup>[23]</sup> are ~140 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in the linear regimes. The on/off ratio is ~10<sup>4</sup>, with a threshold voltage of ~-0.3 V.

To illustrate the extreme level of insensitivity to pinhole type defects, we fabricated transistors on self-assembled monolayers (SAMs) and ultrathin, high-k metal oxide dielectric layers. Figure 6a shows, for example, electrical measurements on a device with t = 100 nm, channel = 7  $\mu$ m, and width = 100  $\mu$ m that uses a trichlorododecylsilane (TDS)

**Figure 6.** a) Electrical characteristics of a transistor that uses a SAM (thickness = 1.9 nm) as a gate dielectric, with channel = 7  $\mu$ m and width = 100  $\mu$ m: typical current-voltage characteristics (left) and linear and log scale plots of transfer curves collected at  $V_D = 0.01V$  (right). b) Electrical characteristics of a transistor that uses a 4.7 nm thick layer of HfO<sub>2</sub> as a gate dielectric, with channel = 5  $\mu$ m and width = 180  $\mu$ m: typical current-voltage characteristics (left) and linear and scale plots of transfer curves collected at  $V_D = 0.01V$  (right).

SAM (thickness ~ 1.9 nm) on the native oxide of a doped silicon wafer. The effective device mobilities are ~120 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in the linear regimes. The threshold voltage is -0.1 V, the on/off ratio is ~10<sup>4</sup>, gate leakage is ~20 nA. The subthreshold slope is 150 mV decade<sup>-1</sup>. Figure 6b shows representative current–voltage and transfer characteristics of a device with a channel length of 5 µm, and channel width of 180 µm that use ultrathin films of HfO<sub>2</sub> (thickness ~ 4.7 nm) formed on a silicon wafer. The effective device mobilities are ~140 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in the linear. The on/off ratio is ~10<sup>5</sup>, with a threshold voltage of ~0.6 V, the subthreshold slope is 100 mV decade<sup>-1</sup> and the gate leakage is ~8 nA. The mobilities of these devices are slightly lower than those of devices with SiO<sub>2</sub> dielectrics. This behavior may result from the relatively low quality of the interfaces.<sup>[24]</sup>

#### 3. Conclusions

This paper describes essential aspects of the mechanics of classes of electronic devices that use solid, printed material nanostructures as components. The results reveal the physics associated with mechanical deformations that can cause these elements to conform to topographical features on the target substrate. As a practical matter, this type of mechanics has the advantage that it reduces greatly the sensitivity of such devices to roughness and other structural imperfections in the substrate or the layers that it supports. The same basic conclusions should also be applicable to other different, but related, types of device strategies that incorporate preformed wires, ribbons, tubes, rods, sheets, and other solid materials.

#### 4. Experimental

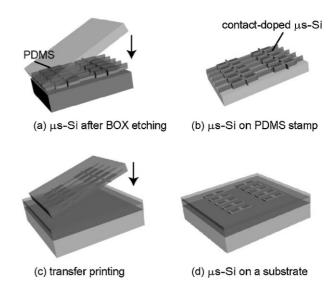

Fabrication of Si Ribbons and Transfer Printing: Figure 7 shows the schematic illustration of steps for creating and then printing µs-Si ribbons with a stamp of PDMS. The fabrication begins with definition of thin ribbons of single-crystal silicon from an SOI (Soitec unibond with 100 or 290 nm top Si layer with doping level of  $6.0 \sim 9.4 \times 10^{14} \text{ cm}^{-3}$ ) wafer. For transistor fabrication, the first step involved phosphorus doping, using a spin-on-dopant (Filmtronics, P509) and a photolithographically defined layer of SiO<sub>2</sub> deposited by plasma enhanced chemical vapor as a doping mask. After the doping steps, SF<sub>6</sub> plasma etching through a patterned layer of photoresist defined the µs-Si ribbons as a part of an interconnected mesh. Undercut etching of the buried oxide with concentrated HF solution (49% in water) released the  $\mu$ s-Si from the wafer. In the next step, contacting a flat elastomeric stamp of PDMS with the interconnected µs-Si ribbons and then peeling back the stamp removed the ribbons from the wafer and left them adhered, by van der Waals forces, to the surface of the stamp (Fig. 7a and b). Contacting the stamp, which now supports the interconnected  $\mu$ s-Si ribbons, to a substrate with a layer of dielectrics and then removing the stamp constituted the printing step (Fig. 7c). After the transfer-printing steps, SF<sub>6</sub> plasma etching through a patterned layer of photoresist defined the isolated µs-Si ribbons (Fig. 7d). These processes yielded arrays of µs-Si ribbons with various dimensions on different substrates, where they were then studied using various techniques as described in the following.

Fabrication of Mechanical Test Structures: Photolithographic techniques were used to pattern lines of epoxy, forming trenches in between, with desired geometries (line widths:  $2 \sim 10 \,\mu$ m, lengths:  $\sim 1 \,\text{cm}$ , and spacings equal to their widths). The process began with spin-casting a precursor (Microchem SU8 diluted with  $1 \sim 30\%$  of SU8-2000 thinner) on Si wafer at  $1500 \sim 5000 \,\text{rpm}$ , prebaking it at 65 and  $100 \,^\circ\text{C}$  for 1 min each, followed by exposing it to UV light for 10 s

Figure 7. Schematic illustration of steps for fabricating and transfer printing interconnected, ultrathin ribbons (i.e.,  $\mu$ s-Si) from a SOI wafer to a substrate.

through a photomask. After post-baking at  $110 \,^{\circ}$ C for 1 min, the unexposed epoxy was removed with SU8 developer, and then cured at  $110 \,^{\circ}$ C for 10 min. The epoxy had thicknesses between 5 and 800 nm. The surface profiles were measured using AFM (DI-3100, Veeco). The test structures were electrically grounded to eliminate electrostatic forces due to charges.

Fabrication of Field Effect Transistor Devices: The devices used bottom gate geometries in which the printed silicon ribbons provided the semiconductor, with dielectric films cast on gate electrodes on the target substrate. Metal electrodes patterned on the silicon provided the source and drain electrodes. Certain experiments used dielectrics with lithographically defined "defects" in the form of circular holes (thickness: 25 nm and hole size: 1 µm diameter) defined using procedures described in previous section. Monolayer dielectrics consisted of TDS (Sigma-Aldrich) SAMs formed by vapor deposition on a layer of oxide on a doped silicon wafer. The thicknesses were 1.9 nm, not including the ~1.4 nm of underlying oxide [25]. High- $\kappa$ dielectrics based on  $HfO_2$  were deposited on p-type silicon (100) substrates using a commercial atomic layer deposition (ALD) reactor (Savannah 100, Cambridge Nanotech.) and Hf(NMe2)4 precursors at a temperature of 250 °C. Before deposition, the substrates were etched in HF to remove the native oxide, and then rinsed in deionized water. The total thickness of the HfO<sub>2</sub> was  $\sim$ 4.7 nm. The capacitance (3.1  $\pm$  0.2  $\mu$ F cm<sup>-2</sup>) was evaluated using by Agilent 4288A capacitance meter.

> Received: February 2, 2008 Published online: August 20, 2008

- R. H. Reuss, B. R. Chalamala, A. Moussessian, M. G. Kane, A. Kumar, D. C. Zhang, J. A. Rogers, M. Hatalis, D. Temple, G. Moddel, B. J. Eliasson, M. J. Estes, J. Kunze, E. S. Handy, E. S. Harmon, D. B. Salzman, J. M. Woodall, M. A. Alam, J. Y. Murthy, S. C. Jacobsen, M. Oliver, D. Markus, P. M. Campbell, E. Snow, *Proc. IEEE* 2005, *39*, 1239.

- [2] J. A. Rogers, Z. Bao, K. Baldwin, A. Dodabalapur, B. Crone, V. R. Raju, V. Kuck, H. Katz, K. Amundson, J. Ewing, P. Drzaic, *Proc. Natl. Acad. Sci. USA* **2001**, *98*, 4835.

- [3] T. Someya, T. Sekitani, S. Iba, Y. Kato, H. Kawaguchi, T. Sakurai, Proc. Natl. Acad. Sci. USA 2004, 101, 9966.

- [4] S. R. Forrest, Nature 2004, 428, 911.

- [5] E. Menard, K. J. Lee, D. Y. Khang, R. G. Nuzzo, J. A. Rogers, *Appl. Phys. Lett.* 2004, 84, 5398.

- [6] A. J. Baca, M. A. Meitl, H. C. Ko, S. M. Mack, H.-S. Kim, J. Dong, P. M. Ferreira, J. A. Rogers, *Adv. Funct. Mater.* **2007**, *17*, 3051.

- [7] Y. Sun, D.-Y. Khang, F. Hua, K. Hurley, R. G. Nuzzo, J. A. Rogers, *Adv. Funct. Mater.* 2005, 15, 30.

- [8] K. J. Lee, J. Lee, H. Hwang, Z. J. Reitmeier, R. F. Davis, J. A. Rogers, R. G. Nuzzo, *Small* 2005, 1, 1164.

- [9] M. A. Meitl, Z.-T. Zhu, V. Kumar, K. J. Lee, X. Feng, Y. Y. Huang, I. Adesida, R. G. Nuzzo, J. A. Rogers, *Nat. Mater.* 2006, 5, 33.

- [10] J.-H. Ahn, H.-S. Kim, K. J. Lee, Z.-T. Zhu, E. Menard, R. G. Nuzzo, J. A. Rogers, *IEEE Electron Device Lett.* **2006**, *27*, 460.

- [11] J.-H. Ahn, H. S. Kim, E. Menard, K. J. Lee, Z. Zhu, D.-H. Kim, R. G. Nuzzo, J. A. Rogers, I. Amlani, V. Kushner, S. G. Thomas, T. Duenas, *Appl. Phys. Lett.* **2007**, *90*, 213501.

- [12] J.-H. Ahn, H.-S. Kim, K. J. Lee, S. Jeon, S. J. Kang, Y. Sun, Nuzzo, J. A. Rogers, *Science* **2006**, *314*, 1754.

- [13] H.-C. Yuan, Z. Ma, M. M. Roberts, D. E. Savage, M. G. Lagally, J. Appl. Phys. 2006, 100, 013708.

- [14] H.-C. Yuan, Z. Ma, Appl. Phys. Lett. 2006, 89, 212105.

- [15] Y. Huang, X. Duan, Q. Wei, C. M. Lieber, Science 2001, 291, 630.

- [16] M. C. McAlpine, H. Ahmad, D. Wang, J. R. Heath, *Nat. Mater.* 2007, 6, 379.

- [17] B. Sun, H. Sirringhaus, Nano Lett. 2005, 5, 2408.

- [18] F. W. Delrio, M. P. de Boer, J. A. Knapp, E. D. Reedy, Jr., P. J. Clews, M. L. Dunn, *Nat. Mater.* 2005, *4*, 629.

- [19] M. P. de Boer, D. L. Luck, W. R. Ashurst, R. Maboudian, A. D. Corwin, J. A. Walraven, J. M. Redmond, J. Microelectromech. Syst. 2004, 13, 63.

- [20] Y. Y. Huang, W. Zhou, K. J. Hsia, E. Menard, J.-U. Park, J. A. Rogers, A. G. Alleyne, *Langmuir* 2005, *21*, 8058.

- [21] D. Bachmann, S. Kuhne, C. Hierold, Sens. Actuators, A 2006, 132, 407.

- [22] M. P. de Boer, T. A. Michalske, J. Appl. Phys. 1999, 86, 817.

- [23] S. M. Sze, *Physics of Semiconductor Devices*, Wiley, New York, USA 1981.

- [24] F. Lime, K. Oshima, M. Cassé, G. Ghibaudo, S. Cristoloveanu, B. Guillaumot, H. Iwai, *Solid-State Electron.* 2003, 47, 1617.

- [25] J. A. Lim, J. H. Cho, Y. Jang, J. T. Han, K. Cho, *Thin Solid Films* 2006, 515, 2079.